上海先进半导体有限公司(上海先进半导体有限公司怎么样)

日期:2023年05月24日 18:24 浏览量:3

(报告出品方/作者:国盛证券,郑震湘、佘凌星、刘嘉元)

一、“超越摩尔定律”,先进封装崛起

1.1 Chiplet:“后摩尔时代”半导体技术发展重要方向

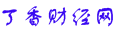

后摩尔时代经济效能提升出现瓶颈,Chiplet 技术应运而生。随着半导体制程节点的持续 演进,短沟道效应以及量子隧穿效应带来的发热、漏电等问题愈发严重,追求经济效能 的摩尔定律日趋放缓。在此背景下,产业开始思考将不同工艺的模块化芯片,像拼接乐 高积木一样的方式用先进封装技术整合在一起,成为一个异构集成芯片,在提升性能的 同时实现低成本和高良率,这就是芯粒(Chiplet)技术。 Chiplet 的概念源于 Marvell 创始人周秀文博士在 ISSCC 2015 上提出的 Mochi(Modular Chip,模块化芯片)架构,伴随着 AMD 第一个将小芯片架构引入其最初的 Epyc 处理器 Naples,Chiplet 技术快速发展。2022 年 3 月,Chiplet 的高速互联标准——UCIe(Universal Chiplet Interconnect Express,通用芯粒互联技术)正式推出,旨在芯片封装层面确立互 联互通的统一标准。

显著降本优势延续摩尔定律。Chiplet 技术迅速发展的原因得益于其在降低成本并提升芯 片性能方面的独特优势,主要体现在以下几个方面:

1) 小面积设计提升芯片良率:传统的良率模型假设缺陷在晶圆上随机散布,并且芯片 上任何地方的缺陷都会使其无法使用,所以大面积芯片比小面积芯片更可能包含缺 陷,造成芯片良率与芯片面积直接相关。一般来说,裸芯(Die)的面积越小,在缺 陷概率一定的情况下,整体的良率就越高。

2) 更低能耗更高性能:在速度方面,采取 3D 封装技术的 chiplet 缩短了线路传输距离, 指令的响应速度得到大幅提升,寄生性电容和电感也得以降低,此外,用更多更密 集的 I/O 接点数,电路密度提升即提高功率密度。3D 封装由于采用更细小、更密集 的电路,信号传输不需要过多的电信号,从而功耗也会相应降低。

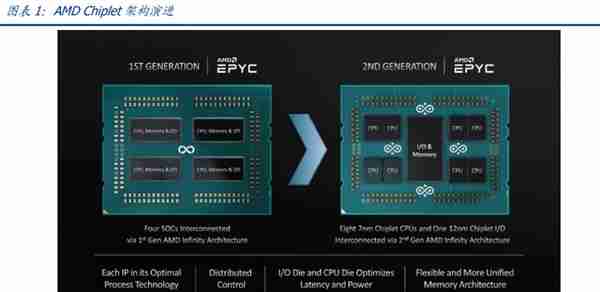

3) IP 快速复用降低设计成本和复杂度,有助于产品快速迭代:随着先进工艺的不断推 进,基于越先进的工艺来设计芯片,其面临的复杂度和设计难度也将大幅提升,同时设计成本也将直线上升。如果在芯片设计阶段,就将大规模的 SoC 按照不同的功 能模块分解为一个个的芯粒,那么部分芯粒则可以做到类似模块化的设计,而且可 以重复运用在不同的芯片产品当中。这样可以极大降低芯片设计的难度和设计成本, 同时也有利于后续产品的迭代,加速产品的上市周期。例如,AMD 在第三代锐龙 (Ryzen)处理器上复用了第二代霄龙(EPYC)处理器的 IOChiplet,这种复用不但 可以将“老旧制程”生产的 Chiplet 继续应用到下一代产品中以节约成本,更能极大 地节约设计、验证和生产周期并降低失败风险。

4) 针对性选取制程工艺降低制造成本:将 SoC 进行 Chiplet 化之后,不同的芯粒可以 根据需要选择合适的工艺来分开制造,然后再通过先进封装技术进行组装,不需要 全部都采用相同制程的工艺在一块晶圆上进行一体化制造,这样可以极大地降低芯 片的制造成本。对于密集封装的逻辑和存储器,7nm 晶体管比 16nm 晶体管便宜, 但 I/O 接口通常具有模拟电路和其他无法从较小节点中受益的大型功能。因此,许 多小芯片设计将 I/O 功能隔离到在旧节点中制造的单独芯片中。一些逻辑电路(例 如加速器)可能不需要以与主处理器相同的最大时钟速率运行,因此可以在中间节 点中制造,使用较旧的工艺技术可以将这些小芯片的制造成本降低多达 50%。

先进制程及超大芯片最受益 Chiplet 技术。综合考虑以上几点优势,The Linley Group 对 Chiplet 技术的经济效益进行过模拟分析,其案例对比中包括一个几乎没有冗余面积 的大芯片(600mm²,80%有效面积)和一个大的有机 BGA 封装(60mm×60mm)被分 成四个相同的小芯片。

摩尔定律减缓带来了小芯片的设计需求,性能提升、成本降低以及大芯片的缺陷问题是 Chiplet 设计成为趋势的三大推动因素。总体来说,Chiplet 是“后摩尔时代”半导体技术 发展重要方向,国外各大厂商持续布局,且均已形成一定规模和应用。据 Omdia 数据, 2018 年全球 Chiplet 市场规模约为 8 亿美元,预计未来随着行业的不断发展,Chiplet 市 场规模有望迎来加速增长。

先进封装市场有望实现高增长。先进封装是实现 Chiplet 的重要方式,根据 Yole,2021 年全球先进封装市场规模 374 亿美金,到 2027 年有望达到 650 亿美金,2021-2027CAGR 10%。从整个封装行业的占比来看,先进封装有望在 2027 年超过 50%,即超过 传统封装的市场规模。先进封装中嵌埋式、2.5D/3D、倒装技术都将实现高复合增速。

1.2 海外龙头先进封装布局如火如荼

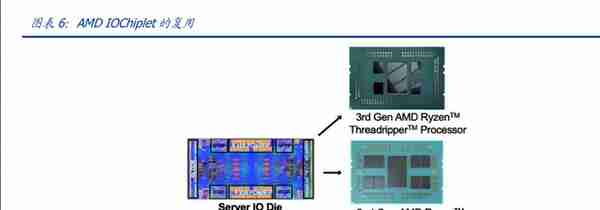

AMD 多年来始终走在封装技术革新前沿。AMD 于 2015 年在 GPU 市场推出高带宽内存 (HBM)和 2.5D 硅中介层技术,引领业界以小尺寸获得最佳内存带宽。在 2017 年引入 MCM 封装技术。2019 年推出了业界首创的基于小芯片的技术,在同一封装内对内核和 IO 使用不同的工艺节点,从而显著提高性能和功能。2021 年宣布与台积电合作开发 3D Chiplet。 AMD 的 3D Chiplet 技术名为 3D V-Cache,实现的关键技术包括硅通孔(TSV)和混 合键合(Hybrid Bonding)。3D V-Cache 使得 AMD 能够在 CPU 上堆叠缓存,首款采用 该技术的产品为 Ryzen 7 5800X3D。其中混合键合技术来自于台积电的 SoIC,使用铜对 铜直接键合,没有任何类型的焊料凸点。因此其连接密度为 2D 封装的 200 倍,互联密 度是微凸块(Micro Bump)的 15 倍,集成度大大提高。

台积电入局先进封装,3DFabric 技术平台势头正盛。台积电于 2011 年开始布局先进封 装,当前其 3DFabric 包含前端 SoIC 技术和后端 CoWoS、InFO 封装技术。

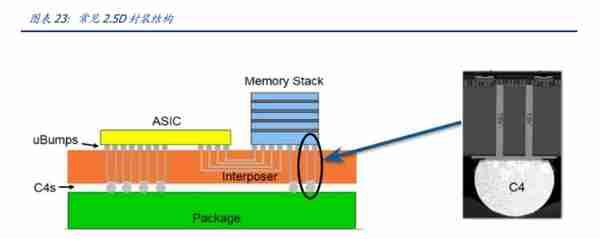

前端芯片堆叠技术,如 chip-on-wafer 和晶圆 wafer-on-wafer,统称为“SoIC”。 其特点是在不实用后段集成中的凸块的情况下,将芯片堆叠在一起。SoIC 的设计实际上 是在创造键合界面,这样芯片就可以直接叠在芯片上面。SoIC 是台积电异构小芯片封装 的关键,具有高密度垂直堆叠性能,与 CoWoS 和 InFO 技术相比,SoIC 可以提供更高的 封装密度和更小的键合间隔。此外,SoIC 还可以与 CoWoS/InFO 共用,基于 SoIC 的 CoWoS 或 InFO 封装将会带来更小的芯片尺寸,实现多个小芯片集成。 CoWoS 发展势头不减,中介层迭代组合助推成本与性能兼具。台积电的 CoWoS 平台包 含 CoWoS-S/R/L,为高性能计算应用提供最佳性能和最高集成密度,提供了广泛的硅中 介层尺寸、HBM 数量和封装尺寸。CoWoS-S 采用硅中介层,可以为高性能计算应用提供 最佳的性能和最高的晶体管密度;CoWoS-R 利用 InFO 技术,利用 RDL 中介层进行互连, 更强调小芯片间的互连;CoWoS-L 结合了 CoWoS-S 和 InFO 技术的优点,使用夹层与 LSI(局部硅互连)芯片进行互连,使用 RDL 层进行电源和信号传输,提供了最灵活的集 成。英伟达、博通、谷歌、亚马逊、NEC、AMD、赛灵思、Habana 等公司已广泛采用 CoWoS 技术。

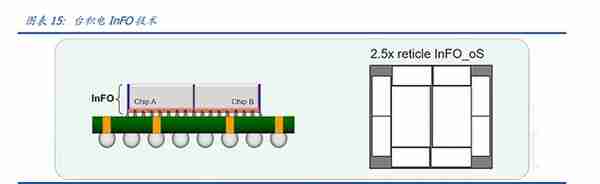

台积电的 InFO 技术使用 polyamide film 代替 CoWoS 中的硅中介层,从而降低成本和封 装高度,这两个因素都是其实现大规模应用的重要条件。InFO 具有高密度的 RDL,适用 于移动、高性能计算等需要高密度互连和性能的应用。台积电的 InFO 分为 InFO_PoP 和 InFO_oS,前者是行业中首款 3D 晶圆级扇出封装,可应用在移动手机的 AP 和 DRAM 上; 后者具有更高密度的 RDL,可集成多个用于 5G 网络的逻辑芯片。相对来说,CoWoS 的 性能更好,但成本较高;InFO 则采用 RDL 代替硅中介层,无须 TSV,性价比更高。

INTEL EMIB 引领低成本 2.5D 异构封装,Foveros 提供高性能 3D 堆叠解决方案。英 特尔的嵌入式多管芯互联桥接封装技术(EMIB)是 2.5D 硅中介层的替代方案,异构集 成模拟设备、内存、CPU、ASIC 芯片以及单片 FPGA 架构,提供了更简单的制造流程、 更高的性能、更强的信号完整性以及更低的复杂性。Foveros 技术是高于 EMIB 技术的 3D 芯片堆叠技术,利用晶圆级封装能力,适用于小尺寸、低功率或有极端内存带宽要求 的情况,包含 Omni 和 Direct 两代扩展。2020 年英特尔发布的 Lakefield 芯片,是首款 基于 Foveros 3D 立体封装技术的芯片,采用 1 个大核+4 个小核的混合 CPU 设计。Intel 预计 Foveros Omni 技术将在 2023 年规模量产。

三星目前主要的先进封装方案包括 I-Cube、X-Cube、R-Cube、H-Cube 四种。 a) Cube:2.5D 硅中介层技术,可将逻辑设备水平连接到 HBM 模块。根据硅中介层的 形式分为两种组装工艺:基板-芯片 CoS(Chip on Substrate)和晶圆-芯片 CoW(Chip on Wafer)。CoS 主要优势可以中间测试,中间测试可以避免在 HBM 模块安装之前 安装任何无效的硅中介层或逻辑芯片。CoW 主要优势是尺寸更大,可以选用较大的 硅中介层。CoS 适用于开发低成本的 2.5D 封装方案,CoW 适用于多 HBM 模块方案。 b) R-Cube:低成本 2.5D RDL 中介层技术,通过高密度 RDL 将逻辑与逻辑、逻辑与 HBM 模块连接,具有更快的周转时间和更好的信号/电源完整性,设计灵活性较好。 c) H-Cube:2021 年 11 月最新推出的 2.5D 封装解决方案,基板整合 ABF 和 HDI,用 于开发大型和低成本的封装。 d) X-Cube:2020 年 8 月推出的 3D 封装方案,包括晶圆-芯片(CoW)、晶圆-晶圆 (WoW)和硅通孔(TSV)技术,实现高密度高性能封装。

先进封装作为 Chiplet 的重要部分,其四大要素分别为 RDL(Re-distributed layer,重布 线层)、TSV(Through Silicon Via,硅通孔)、Bump(凸点)和 Wafer(晶圆),RDL 起 到 XY 平面电气延伸的作用,TSV 起到 Z 轴电气延伸的作用,Bump 起到界面互联和应力 缓冲的作用,Wafer 作为集成电路的载体以及 RDL 和 TSV 的介质和载体。接下来我们围 绕这四大要素,讨论关键工艺相关的设备、材料供应链。

二、RDL 重布线——晶圆级封装关键工艺

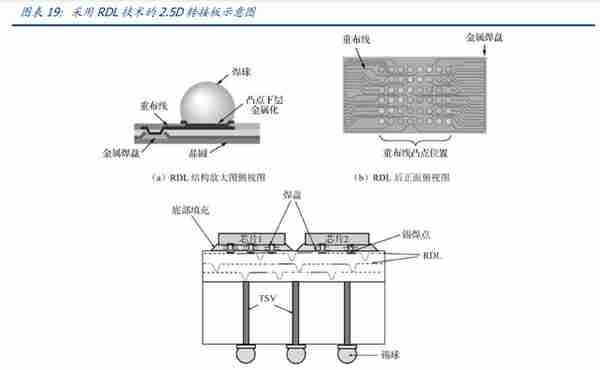

RDL(Re-distributed layer,重布线层)技术是晶圆级封装关键技术。由于在设计芯 片时只有极少数芯片的 I/O 端口是按照面阵列形式来进行设计的,因此需要重布线技术, 在晶圆表面利用金属层与介质层形成相应的金属布线图形,将原来设计的芯片线路焊盘 重新布线到新的、间距更宽的位置,使芯片能适用于更有效的封装互连形式。RDL 可以 改变线路 I/O 端口原有的设计,加大 I/O 端口间距,提供较大的凸块焊接面积,减小基 板与元器件间的应力,提高元器件的可靠性。此外封装工艺 RDL 可取代部分芯片线路, 以缩短芯片开发时间。

在晶圆级封装中,RDL 是最为关键的技术,通过 RDL 将 IO Pad 进行扇入 Fan-In 或者扇 出 Fan-Out,形成不同类型的晶圆级封装。在 2.5D IC 集成中,除了硅基板上的 TSV,RDL 同样不可或缺,以台积电 CoWoS-S 为例,其在中间层上下都布有宽间距的 RDL 层, 通过 TIV(Through interposer Via)进行信号和电气传递,在高速传输中提供低损耗的 高频信号。

在 3D IC 集成中,对于上下堆叠是同一种芯片,通常 TSV 就可以直接完成电气互联功能 了,而堆叠上下如果是不同类型芯片,则需要通过 RDL 重布线层将上下层芯片的 IO 进 行对准,从而完成电气互联。随着工艺技术的发展,通过 RDL 形成的金属布线的线宽和 线间距也会越来越小,从而提供更高的互联密度。 RDL 工艺流程:RDL 的制作方式包括电镀、大马士革、金属蒸镀+金属剥除等,其中利 用前道晶圆制造里面的大马士革原理的 RDL 工艺可以满足低线宽/间距(Line/Space, L/S)的 RDL 结构。

三、TSV 硅通孔——2.5D/3D 封装关键工艺

由于当前不同厂商集成技术路线存在差异,2.5D 封装工艺和技术其实并没有一个统一的 标准,通常可以将 2.5D 封装理解为,多芯片之间通过中介层、硅桥、高密度 RDL 等方 式进行互连的封装方式。其核心包括 1)多芯片集成;2)互连部分引入高 I/O 密度的介 质而不是在依靠载板上走线。

中介层是 2.5D 封装关键特点之一。中介层用来连接多个芯片,目前中介层主要是硅基 材质。DRAM 和 CPU、CPU、SoC 等芯片通过硅中介层实现高速的运算和数据交流,降 低功耗,提升效率。常见的 2.5D 封装技术在硅中介层有 TSV 集成,芯片通常通过 MicroBump(微凸块)和中介层相连接,作为中介层的硅基板采用 Bump 和基板相连, 硅基板表面通过 RDL 布线,TSV 作为硅基板上下表面电气连接的通道,这种 2.5D 集成 适合芯片规模比较大,引脚密度高的情况,芯片一般以 FlipChip 形式安装在硅基板上。

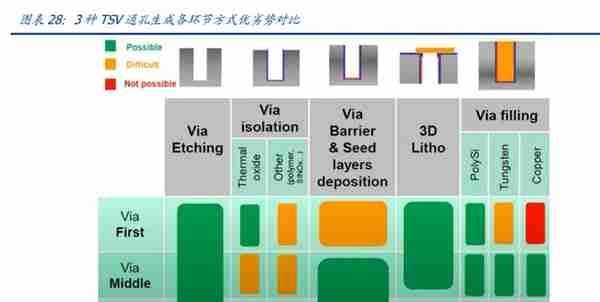

TSV 技术是 2.5D/3D 封装的关键工艺之一。硅通孔技术(TSV,Through Silicon Via) 是通过在芯片和芯片之间、晶圆和晶圆之间制作垂直导通,实现芯片之间互连的技术。 TSV 技术通过铜、钨和多晶硅等导电物质的填充,实现硅通孔的垂直电气互连。硅通孔 技术的优势是可以通过垂直互连减小互连长度、信号延迟,降低电容、电感,实现芯片 间的低功耗、高速通讯,增加带宽和实现器件集成的小型化。 Via-Middle 和 Via-Last 是较为常见的通孔方式。依据 TSV 通孔生成的阶段 TSV 工艺 可以分为:1)Via-First;2)Via-Middle;3)Via-Last。 1) Via-First 指的是 TSVs 在 FEOL 工艺(例如晶体管)之前制造。Via-First 由于是在 器件制造之前进行通孔工艺,因此可以使用高温工艺来制造绝缘层,其劣势在于 填充通孔的材料受限,由于后续晶体管制造过程中会有高温的环节,此时如果填 充材料为铜的时候,铜会很容易扩散到硅材料中。 2) Via-Middle 指的是 TSVs 在 FEOL 之后,BEOL(例如金属层)之前制备,这种工 艺由于晶圆厂在设备能力方面具备优势,晶圆厂通常也会制造,但也有部分 OSAT 厂商可以完成这一工艺。Via-Middle 的优势在于可以实现较小的 TSV 结构间距, 再布线层通道阻塞小以及 TSV 结构电阻也会较小,其劣势主要在于它必须适合 产品器件性能要求这样才不会干扰器件,并且也不会干扰相邻的布线层。 3) Via-Last 指的是 TSVs 在 FEOL,MOL 和 BEOL 工艺之后制造 TSV,Via-Last(从 晶圆正面)的方式由于在刻蚀的时候除了刻蚀硅之外,还需刻蚀整个电介质层, 以及会阻塞布线通道,因此较少被使用。Backside Via-Last 从晶圆背面进行通孔, 可以简化工艺流程,背面后通孔工艺被广泛用于图像传感器和 MEMS 器件。

TSV 工艺主要包括深硅刻蚀形成微孔,再进行绝缘层、阻挡层、种子层的沉积,深孔填 充,退火,CMP 减薄,Pad 的制备叠加等工艺技术。

1) 孔成型:孔成型的方式有激光打孔、干法刻蚀、湿法刻蚀多种。随着 TSV 的空径 减小、深宽比增加,基于深硅刻蚀(Deep Reactive Ion Etching,DRIE)的 Bosch 工艺是目前应用最广泛工艺。反应离子刻蚀(Reactive Ion Etching,RIE)工艺 是采用物理轰击和化学反应双重作用的刻蚀,Bosch 工艺通过刻蚀和保护两个步 骤交替进行来提高 TSV 的各向异性,保证 TSV 通孔的垂直度。 设备及材料:深硅刻蚀需要的设备是感应耦合高密度等离子体干法刻蚀机 (Inductively Coupled Plasma Etcher,ICP),深硅刻蚀的发展方向是精细深槽、 高深宽比微纳通孔的高精度,目前全球主流的深硅刻蚀设备由应用材料、泛林集 团等厂商垄断,目前国内中微公司、北方华创等在这一领域进步迅速。Bosch 工 艺过程中主要需要的气体是氟基气体,全球供应商包括法液空、默克、林德等。

2) 沉积绝缘层:TSV 孔内绝缘层用于实现硅村底与孔内传输通道的绝缘,防止 TSV 通孔之间漏电和串扰。TSV 孔内绝缘层的质量将直接影响 TSV 硅转接板的信号 完整性和电源完整性,是保证 2.5D TSV 转接板性能的关键工艺之一。在 TSV 孔 刻蚀和深孔清洗完毕后,在 TSV 孔壁沉积绝缘材料形成孔壁介质绝缘层,孔壁 绝缘介质层需要完全覆盖 TSV 孔的内壁和 TSV 硅转接基板表面以达到良好的绝 缘性能。TSV 孔壁绝缘介质材料选用无机介质材料,如二氧化硅、氮化硅、或二 氧化硅和氮化硅构成的复合材料。 设备:目前 TSV 孔壁无机绝缘介质材料的常用制各方法包括 PECVD、SACVD、 ALD 和热氧化法。PECVD 可以实现较低的沉积温度,如 200℃以下,但对于孔径 较小且深宽比较大的垂直 TSV 孔的孔璧合阶覆盖率不足;SACVD 的孔壁台阶覆 盖率优于 PECVD,但沉积温度较高,通常在 400℃及以上;ALD 的孔壁台阶覆盖 率能达到 80%以上,但沉积速度较慢;热氧化法制备的二氧化硅层结构致密、孔 壁台阶覆盖率高,但热氧化工艺温度通常都在 1000℃以上,此外热氧化工艺可 以在一炉中同时氧化多片,成本较低。海外 KLA(2019 年收购 Orbotech,Orbotech 2014 年并购 SPTS,SPTS 在先进封装领域的 PVD、CVD 设备领域综合技术实力 领先)、应用材料等供应商技术领先,国内拓荆科技等公司在这一领域进展亮眼。

3) 沉积阻挡层/种子层:在 2.5D TSV 中介层工艺中,一般使用铜作为 TSV 通孔内 部金属互联材料。在电镀铜填充 TSV 通孔前,需要在 TSV 孔内制备电镀阻挡/种 子层,一般选用 Ti、Ta、TiN、TaN 等材料。TSV 电镀种子层起着与电镀电极电 连接并实现 TSV 孔填充的作用。 设备:通常用物理气相沉积(PVD)法制作阻挡层和种子层绝缘层,为后续的铜 填充做好准备。后续的电镀铜填充要求 TSV 侧壁和底部具有连续的阻挡层和种 子层。种子层的连续性和均匀性被认为是 TSV 铜填充最重要的影响因素。根据 硅通孔的形状、深宽比及沉积方法不同,种子层的特点也各有不同,种子层沉积 的厚度、均匀性和粘合强度是非常重要的指标。海外 KLA(SPTS)同样在先进封 装领域的 PVD 全球市占率较高,北方华创凭借强劲实力,国内份额不断提升。

4) 电镀填充工艺:TSV 深孔的填充技术是 3D 集成的关键技术,也是难度较大的一 个环节,TSV 填充效果直接关系到后续器件的电学性能和可靠性。从填充材料角 度,可以填充的材料包括铜、钨、多晶硅等,目前电镀铜工艺是主流的先进封装 中硅通孔填充材料。硅通孔电镀铜工艺目前主要有大马士革电镀和掩模电镀两种。 设备:深孔金属化电镀设备用于新一代高频组件高深宽比通孔填孔电镀铜工艺, 解决高深宽比微孔内的金属化问题,提高互联孔的可靠性。由于电镀铜在 TSV 工 艺中的重要性非常高,对设备的要求比较高,成熟的用于 TSV 填孔镀铜的设备 价格昂贵。目前电镀设备主要有德国安美特(Atotech,全球领先的化学品和电镀 解决方案供应商,2022 年正式被美国 MKS Instruments 万机仪器收购),东京电 子、Ebara、应用材料、泛林集团等厂商垄断。

电镀液:在硅通孔电镀中,大马士革电镀、掩模电镀或其他电镀方式所需的电镀 液材料体系都基本相同。硅通孔电镀液主要的成分包含电镀原液(或称为基础镀 液)和添加剂。硅通孔电镀液的主要作用是为硅通孔的电镀填充提供充足的铜离 子和良好的电镀环境,通过在电镀液中加入各种添加剂可以改善硅通孔的电镀质 量,从而提高电镀填充的效果。目前海外主要的硅通孔电镀液材料供应商包括陶 氏化学、乐思化学(Enthone Chemical)、上村(Uyemura)、安美特(Atotech)、 罗门哈斯(Rohm&haas)等,国内上海新阳在这一领域亦有突破。

5) CMP(化学机械抛光)工艺和背面露头工艺:由于 TSV 中介层还需要高密度多 层再布线,CMP 技术引入到 TSV 制程中,用于去除硅表面的二氧化硅介质层、 阻挡层和种子层。TSV 背面露头技术也是 2.5DTSV 转接基板的关键工艺,包括 晶圆减薄、干/湿法刻蚀工艺。随着晶圆厚度越来越小,散热性提升,与此同时 TSV 深度随之减小,带来互联延迟和损耗的减少。然而晶圆厚度变薄的同时,材 料内部的应力会随着减薄工序的进行而增大使得硅片产生翘曲、粗糙和断裂等缺 陷。2.5D TSV 转接基板背面减薄之后,一般还需要通过干法或者湿法刻蚀工艺, 从背面露出 TSV 铜柱,从而实现后续晶圆背面的电信号连接。 设备及材料:考虑应力等问题,目前业界多采用一体机的思路,将晶圆的磨削、 抛光、贴片等工序集合在一台设备中。海外龙头包括应用材料、Ebara 等。材料 方面 CMP 材料全球主要供应商包括陶氏、FujiFilm、卡博特等,国内鼎龙股份、 安集科技已经在 CMP 抛光垫、抛光液领域实现国产化突破。TSV、FOWLP 等先 进封装技术带来对 CMP 步骤的增加,进而增加了 CMP 耗材需求量。

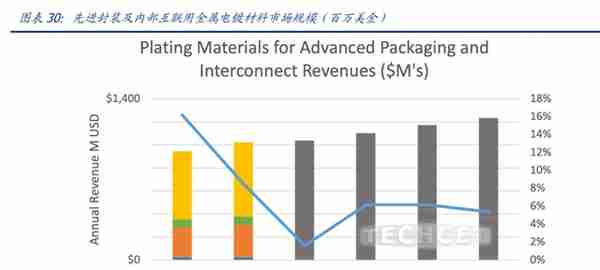

6) 晶圆减薄:在 via first 和 via middle 工艺中,晶圆表面平坦化后,还需要进行晶 圆背面的减薄使 TSV 露出,via last 工艺中,晶圆在进行 Bosch 刻蚀工艺前就会 进行减薄。晶圆减薄的目的是使 TSV 露出,在晶圆级多层堆叠技术中,需要将多 片晶圆进行堆叠键合,同时总厚度还必须满足封装设备的要求。目前较为先进的多层堆叠使用的芯片厚度均在 100μm 以下。未来如果需要叠加更多层,芯片的 厚度需减薄至 25μm 甚至更小。传统的晶圆减薄技术包括机械磨削、CMP 和湿 法腐蚀等。由于晶圆经过减薄后容易产生变形或翘曲,目前业界主流的解决方案 是采用一体机的思路,将晶圆的磨削、抛光、保护膜去除和划片膜粘贴等工序集 合在一台设备内。晶圆从始至终都被吸在真空吸盘上,始终保持平整状态,从而 防止了晶圆在工序间搬运时产生变形或翘曲。 先进封装驱动 CVD 沉积、电镀及溅射靶材市场持续增长。根据 TECHCET,2022 年溅射 靶材、ALD/CVD 前驱体和金属化学品等沉积材料全球市场规模年接近 39 亿美元,预计 2023 年超过 41 亿美元,到 2026 年市场规模达到 47 亿美金。其中 2022 年金属电镀市 场规模超过 11 亿美金,预计到 2026 年将超过 13 亿美金。市场规模的持续增长主要得 益于使用 RDL、TSV 和铜凸点结构的先进封装需求提升。

四、临时键合——超薄晶圆支撑系统

超薄晶圆具有降低封装整体厚度、增强散热、增强电学性能、提高集成度等优势,在先 进封装中被广泛使用。根据 Yole,2025 年全球超薄晶圆市场规模有望超过 1.35 亿片(等 效 8 英寸)。然而由于超薄晶圆柔性较差且易碎,容易产生翘曲,需要一套支撑系统来防 止这些损伤。通常在封装前使用某种特定的中间层材料,将超薄晶圆临时键合到一个晶 圆载板上,这种工艺称为临时键合工艺(Temporary Bonding)。

按照工艺流程来分,目前主要有热/机械滑移式临时键合与解键合、热/机械滑移式临时 键合与解键合、激光式临时键合与解键合三种工艺。其中激光临时键合与解键合工艺最 大工艺温度高,抗化学性好,是最新一代的临时键合/解键合技术方案。

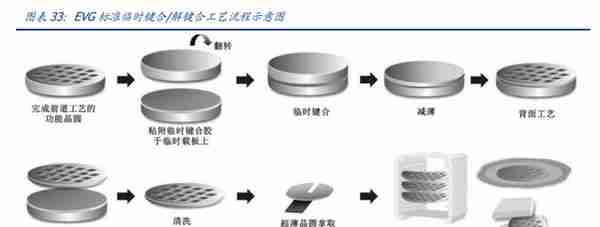

临时键合/解键合常见工艺流程:首先在临时载板或功能晶圆上通过压合、粘贴或旋涂等 方法制造一层中间层材料作为键合黏接剂,然后翻转功能晶圆,使其正面与临时载板对 准,然后将二者转移至键合腔进行键合,临时键合完成后,对功能晶圆进行减薄,一般 包括机械研磨、化学抛光等步骤。减薄后再进行深硅刻蚀、扩散阻挡层及种子层沉积、 电镀、机械化学抛光、光刻、刻蚀、金属化等背面加工,形成再布线层、TSV 等结构。 最后可以采用不同方式的解键合工艺将功能晶圆与临时载板分离,对二者分别进行清洗后,将功能晶圆转移到划片膜或其他支撑系统中,以便进行下一步工艺,临时载板则可 以马上进行再次利用。在这一工艺流程中,仅添加了临时键合机与解键合机两台设备, 其他步骤均可采用与标准晶圆制造相同的设备与工艺完成。目前全球临时键合设备主要 供应商有 EV Group、SUSS MicroTec 等公司。

根据 Yole,2020 年“超越摩尔定律”相关的键合设备市场规模达到 17 亿美金,预计到 2027 年将达到 28 亿美金。其中 2020 年临时键合设备市场规模为 1.13 亿美金,预计 2027 年将达到 1.76 亿美金,SUSS 在全球占据主导地位。

临时键合胶:是把功能晶圆和临时载板黏接在一起的中间层材料。不同工艺对应的临时 键合在键合方法、键合工艺和材料选择上有所不同。对于临时键合胶的选择,需要关注 热稳定性、化学稳定性、粘接强度、机械稳定性、均一性等因素。临时键合胶的材料性 能主要是由基础黏料的性质决定的,因此基础黏料的选择至关重要。可用作基础黏料的 高分子聚合物材料包括热塑性树脂、热固性树脂、光刻胶等。

目前全球临时键合胶产品主要有海外供应商垄断,主要有 Brewer Sciences 的 WaferBond 和 ZoneBond 系列产品、3M 的 LTHC 系列产品、DuPont 的 HD-3000 系列产品、Thin Materials 的 T-MAT 系列产品、Dow Corning 的 WL 系列产品、东京应化工业株式会社 (TOK)的 Zero Newton 系列产品和 Dow Chemical 的 Cyclotene 系列产品。

五、微凸点、底部填充与混合键合技术

5.1 凸点技术——间距缩小、密度提升

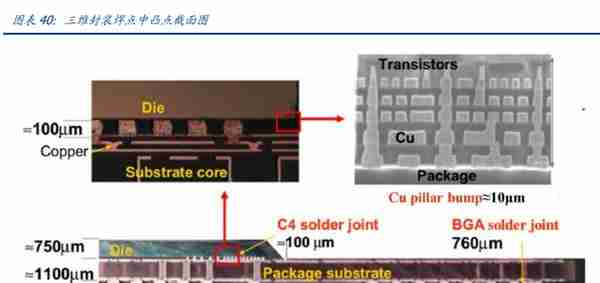

凸点作为封装结构中的重要一环,为堆叠芯片及固定装配提供所需的机械支撑,并实现 芯片与中介层,芯片与芯片间的电气互连。凸点的发展趋势是尺寸不断缩小,从球栅阵 列焊球(Ball-Grid-Array Solder Ball,BGA ball),其直径范围通常在 0.25-0.76mm,到倒 装凸点(Flip-Chip Solder Bump,FC Bump),也被称为可控塌陷芯片焊点(Controlled Callapse Chip Connection solder joint,C4 solder joint),其直径范围通常在 100-150μ m,再到微凸点(micro bump),其直径可小至 2μm。微凸点可以通过光刻电镀的方法 在整片晶圆上进行大规模制备,生产效率高,并且降低批量封装成本。按照凸点的结构, 微凸点可以分为焊料凸点、铜柱凸点和键合铜凸点。

焊料凸点是目前倒装封装互连凸点的主流选择。焊料凸点(Solder Ball Bump,SBB)一 般为锡基的焊料形成的凸点,材料成分包括纯 Sn 及 Sn-Pb、Sn-Cu、Sn-Ag、Sn-Zn 和 Sn-Bi 等体系的合金。由于组装工艺非常简单,目前焊料凸点应用非常广泛。由于近年来 人们环保意识提高,元器件无铅化趋势显著,无铅焊料被越来越多的使用,由于无铅焊 料在铺展能力和润湿性方面有不足,助焊剂作为辅助材料,与无铅焊料配套使用,需求 量持续增长。

铜柱凸点将成为高密度、窄节距集成电路封装市场主流方式。随着先进封装对凸点间距 要求越来越小,为了避免桥接现象的发生,实现更高 I/O 密度,IBM 公司于 21 世纪初首 次提出了铜柱凸点,申请了铜柱凸点结构的相关专利。在焊料互连过程中,铜柱凸点能 够保持一定的高度,既可以防止焊料的桥接现象发生,又可以掌控堆叠层芯片的间距高 度,铜柱凸点的高径比不再受到阵列间距的限制,在相同的凸点间距下,可以提供更大 的支撑高度,大大改善了底部填充胶的流动性。 电镀法是凸块制作使用最广泛的方式。凸块制作技术包括电镀法、化学镀法、蒸发法和 锡膏印刷法等,但以电镀的方法应用最为广泛,因为其可以做到更小的尺寸,达到更高 的生产效率及更好的可靠性。借助光刻掩膜技术的电镀法则具有更高的制备精度,可实 现凸点在晶圆上的直接制备,适合铜柱凸点的制备。

回流焊仍为凸点键合主流方式,TCB 潜力大。根据铜柱凸点的节距不同,铜柱凸点的键 合方法可以分为回流焊和热压键合(TCB)两种方式。对于节距较大的铜柱凸点,可采用 回流焊方式完成凸点键合。回流焊的方式效率高,成本低,其缺点跟热膨胀系数(CTE) 有关,由于整个封装由不同的材料组成,在回流炉中加热会导致这些不同的材料以不同 的速度膨胀。当芯片和基板膨胀和冷却时,CTE 的差异会导致翘曲。此外还会有芯片间 隙变化等问题导致最终产品电气性能差。

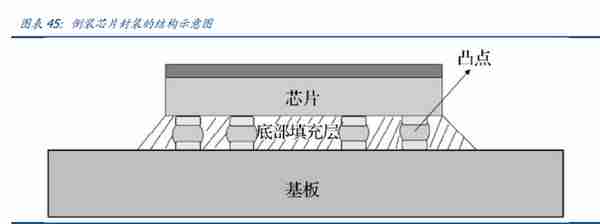

5.2 底部填充工艺——分散应力提升可靠性

底部填充是芯片倒装于基板封装结构中的重要工艺。其作用是 1)将芯片凸点位置的集 中应力分散到底部填充体和塑封料中;2)可阻止焊料蠕变,并增加倒装芯片连接的强度 与刚度;3)保护芯片免受环境的影响,如湿气、离子污染等;4)使芯片抗机械振动与 冲击;5)极大改善焊点的热疲劳可靠性。

目前,全球 NCP 的主要供应商有汉高(Henkel)、纳美仕(Namics)、长濑产业株式会社 (Nagase)、日立化成(Hitachi Chemical)、松下(Panasonic)。NCF 的供应商主要包括 汉高(Henkel)、日立化成(Hitachi Chemical)、日东电工(Nitto Denko)、纳美仕(Namics)、 住友(Sumitomo)。

5.3 混合键合技术——赋能 3D 堆叠

当凸点储存进一步缩小到小于10~20um时,焊锡球成为了工艺难点及缺陷的主要来源。 业界相应提出了 Hybrid Bonding 工艺,可以解决 bump 间距小于 10 微米芯片间的键合 问题,以实现更高的互连密度,此外 Hybrid Bonding 信号丢失率几乎可以忽略不计,在 高吞吐量,高性能计算领域优势明显。

混合键合(Hybrid Bonding)也称为 DBI(Direct Bond Interconnect,直接键合连接), Sony 最早在 CIS 中运用了混合键合技术,公司 2016 年将这一技术用于 Samsung Galaxy S7 的背照式 CIS(BI-CIS)中,大幅提高了镜头分辨率。

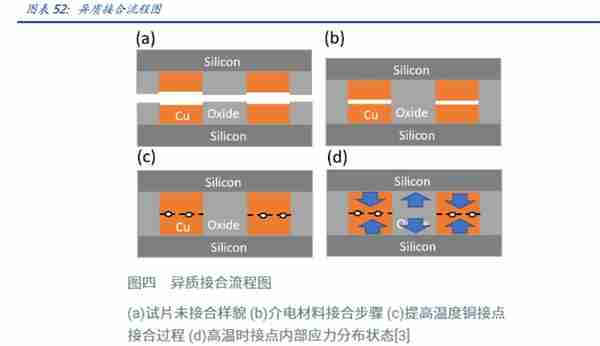

混合键合中晶圆到晶圆(W2W)的工艺从晶圆加工到最终的 BEOL 互连级别开始。沉积 合适的电介质(SiON、SiCN 或 SiO2),然后将其蚀刻以在下面的金属上形成通孔。沉积 阻隔层和种子层,然后镀铜。铜 CMP 抛光覆盖层,这样使得后续在退火时铜膨胀时,表 面微小的间隙可以被填补。紧接着清洗晶圆去除所有污染物,然后通过等离子体活化, 在电介质上产生活性位点。两个晶圆在键合机精确对齐,之后在退火炉中,铜熔合在一 起,进行电接触。最后,晶圆边缘修整之后是背面晶圆研磨减薄圆,清洁和 CMP 抛光等, 并用表面声学显微镜(SAM)检查粘合晶圆中的空隙。

Hybrid Bonding 技术优势显著,各大头部厂商重视布局,但其生产成本仍然非常昂贵。 Cu 的熔点(1083℃)高、自扩散速率低,难以实现低温键合,Cu-Cu 直接键合需要在 400℃的高温下才能充分发生原子扩散,高温会降低对中精度、损伤器件性能、增加设备 要求等问题。目前实现 Cu-Cu 低温键合的方式主要为热压键合(TCB),混合键合工艺、 纳米材料烧结工艺等。总体来讲各项工艺仍处于不断发展进步阶段。

六、IC 载板——集成电路核心封装材料

IC 载板:简而言之,是 IC 的载体,建立起 IC 与 PCB 之间的讯号链接;同时可以保护电 路、固定线路、并起到一定的散热能力。根据材料及应用的不同,封装基板可以分为陶 瓷基板、金属基板、有机基板及硅/玻璃基板(中间层)等。其中有机基板具有厚度薄、 线路密、对位精度要求高、电气结构更复杂等特点,在高功能集成电路 I/O 端口数不断 增加,对散热性要求不断提高的背景下,有机基板逐渐向多层化、薄型化和高密度化发 展,广泛用于计算机、通信产品、消费类电子及汽车电子产品等领域。 刚性有机基板按照制板工艺分类,刚性有机基板可分为层压(Lamination)基板和积层 (Build-up)基板两大类。I/O 端口数较多的高密度封装器件需要采用积层基板,其关键 工艺是微孔技术,先在芯板两侧对称制造绝缘层,然后通过光刻或激光钻孔的方式在绝 缘层上形成微孔,后续通过镀铜填充微孔,并在绝缘层表明形成电路图形,重复这些积 层步骤可以制造多积层板。另外,在基板制造过程中需要用到的绝缘层材料目前主流是 日本味之素精细化学品公司生产的 ABF(Ajinomoto Build-up Film)。

高端封装基板海外垄断,国产进展迅速。目前全球封装基板供应商主要来自日本、韩国 和中国台湾地区。其中以揖斐电株式会社(Ibiden)、新光电气工业株式会社(Shinko)、 京瓷集团(Kyocera)等为代表的日本公司技术实力非常强,占据有机基板主要市场,的 三星电机(SEMCO)、信泰(Simmtech)和中国台湾的南亚科技(Nanya Technology)、 欣兴电子(Unimicron)等公司由于具有产业链的优势,占据着市场中的重要份额。中国 大陆地区封装基板产业由于起步较晚,加之在关键原材料、设备及工艺等方面的差距, 因此目前在技术水平、工艺能力及市场占有率上相较日本、韩国和中国台湾地区的知名 封装基板产业仍然处于落后地位。在内资企业中,兴森科技、深南电路、珠海越亚、安 捷利等公司技术实力强劲。 根据 Yole,2021 年全球先进封装基板市场规模 157 亿美金,预计 2027 年有望增长 到 296 亿美金。2021 年 ABF 载板全球市场规模 48 亿美金,前五大厂商揖斐电、欣兴 电子、南亚科技、新光电气和 AT&S 占据了全球接近 75%的份额。

七、核心公司

7.1 华峰测控:国内测试设备龙头,新品发力进行时

华峰测控是一家聚焦模拟和混合信号测试设备企业,主要面向集成电路封测、晶圆制造 和集成电路设计企业等客户。公司主要产品为半导体自动化测试系统和测试系统配件, 公司的测试系统包括 STS8200 系列、STS8250 系列和 STS8300 系列等;测试系统配件 主要包括浮动 V/I 源表、时间测量、数字测量、及电器控制、交流 V/I 源表等关键测试 模块。 华峰测控发布 2022 年业绩快报。公司预计 2022 年全年实现营收 10.71 亿元, yoy+21.89%,归母净利润 5.25 亿元,yoy+19.67%,扣非归母净利润 5.06 亿元, yoy+16.38%。2022 年受大环境影响,叠加半导体市场景气度持续低迷,给公司业绩增 长带来挑战,华峰测控坚持既定的发展策略,不断优化产品结构,同时加强新产品研发 和市场开拓,提高产品市占率,保证了业务的持续稳定增长。

公司研发效率及产品力较强。公司在传统模拟混合领域国内领先,产品竞争力强,具有 较高的装机存量和客户服务基础;在新兴应用领域(GaN、PIM)获取先机,具有较强竞 争力;在更大的 SoC 测试市场持续发力,迭代测试板卡增加覆盖目标市场,打开 soc 测 试国产替代空间。 新品客户拓展顺利,持续迭代巩固核心竞争力。公司 2022 年下半年订单在设计公司和 封测厂均有较好表现,且订单以 8300 产品为主。STS8200 已内部迭代多次,随着装机 量的不断提升,应用范围的不断拓展,已经成为了模拟、混合和功率器件测试的经典平 台,未来还将不断迭代;STS8300 从推出至今已有 3 年,客户拓展顺利,装机量也在不 断增加,客户生态圈构建进展顺利,内部资源板卡也在加速迭代,应用范围也在不断拓 展。下一代 SoC 测试设备基本系统已经完成,资源板卡也在研发中。

7.2 长川科技:测试新品厚积薄发,内生外延铸平台龙头

长川科技成立于 2008 年 4 月,并于 2017 年 4 月在深交所创业板上市,主要从事集成电 路专用设备的研发、生产和销售,主要产品包括测试机、分选机、探针台、AOI 设备和 自动化设备。公司自成立以来始终专注于集成电路测试设备领域,行业深耕多年,掌握 集成电路测试设备相关核心技术,技术水平领先。公司致力于提升我国半导体装备技术 水平、积极推动行业升级,长川科技先后被认定为软件企业、国家级高新技术企业、浙 江省重点企业研究院、省级高新技术企业研究开发中心、杭州市企业高新技术研究开发 中心。

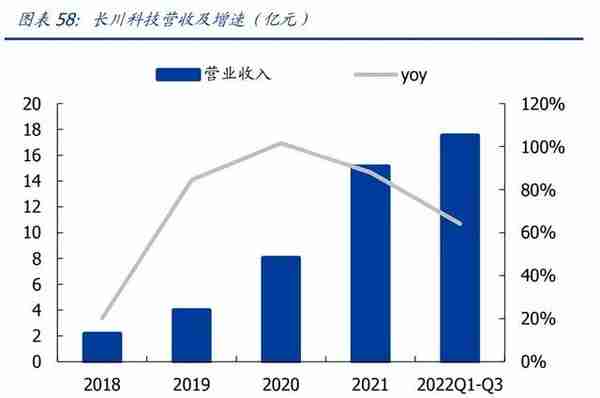

营收延续增长,盈利水平稳步攀升。长川科技 2022 年前三季度实现营收 17.54 亿元, yoy+64.09%,归母净利润 3.25 亿元,yoy+151.33%,扣非归母净利润 2.62 亿元, yoy+134.44%,前三季度综合毛利率 54.06%,同比+2.63%,归母净利率 18.56%,同 比+6.44%。公司 2022Q3 单季度实现营收 5.65 亿元,yoy+42.91%,归母净利润 0.8 亿 元,yoy+101.13%,单季度毛利率 50.38%,归母净利率 14.22%。此外,公司预计 2022 年全年实现归母净利润 4.5-5.2 亿元,同比增长 106.2%-138.3%。 公司持续研发并积极拓展新品及市场、与业内知名客户的深度合作,有效提升公司市场 竞争力,业务规模稳步扩大。此外,公司持续优化客户结构,高端品类收入占比持不断 上升,营业收入和净利润的增长率始终维持在较高水平。

分产品来看,2021 年和 2022H1,公司测试机分别实现收入 4.89 亿元和 4.79 亿元,同 比增长 174.3%和 90.2%,2022 年上半年销售收入就接近 2021 年全年水平。分选机方 面,公司生产的分选机包括重力式分选机、平移式分选机、测编一体机等。2021 年和 2022H1 分别实现营收 9.4 亿元和 6.4 亿元,同比增长 67.6%和 68.4%。此外公司其他 业务(设备相关配件销售及设备维护等)2021 年和 2022H1 分别实现营收 8,566.8 万元 和 6,711.1 万元,同比增长 28.3%和 68.4%。

围绕市场需求推进研发创新,研发投入持续增长。长川科技 2022 年前三季度研发费用 4.5 亿元,同比增长 95%,占营收比重 25.7%,公司研发费用率始终保持较高水平。围 绕数字测试机、分选机等产品,公司拓展中高端市场,实现营收高速增长,产品结构持 续改善。截至 2021 年底,公司研发人员 925 人,研发人员数量占比 54.9%,人均创收 89.7 万元。

半导体测试系统市场趋势向上,SoC 类和数字集成电路测试设备占比较高。根据 SEMI, 2022 年全球 IC 测试设备市场规模预计为 87.8 亿美金,分产品来看,根据 SEMI,2018 年国内 IC 测试设备市场规模约 57.0 亿元,测试机/分选机/探针台分别占比 63.1%/17.4%/15.2%。2020 年中国大陆 IC 测试设备市场规模 91.4 亿元,2015-2020 年 CAGR 达 29.3%,高于同期全球水平。随着我国集成电路产业规模不断扩大以及全球 产能向我国大陆地区加快转移,集成电路各细分行业对测试设备需求还将不断增长,国 内 IC 测试设备市场需求上升空间较大。 海外厂商主导全球半导体测试设备市场,国产替代空间广阔。集成电路检测在测试精度、速度、效率和可靠性等方面要求高。全球先进测试设备制造技术基本掌握在美国、日本 等集成电路产业发达国家厂商手中,市场格局呈现泰瑞达、爱德万、科休等厂商寡头垄 断。根据 SEMI,泰瑞达、爱德万两家公司半导体测试设备合计占全球测试机市场份额超 过 66%。通过打入国内测试龙头企业,长川科技、华峰测控等实现了部分半导体测试设 备国产替代,但营收体量相比海外龙头泰瑞达、爱德万近年来年收入规模超过 25 亿美 金,长川科技收入规模小于 5 亿美金,仍有较大替代空间。

内生外延打造半导体测试设备综合供应商。长川科技经过多年研发和积累,目前已成为 国内领先的集成电路专用测试设备供应商,产品获得了长电科技、华天科技、通富微电、 士兰微、华润微电子、日月光等多个一流集成电路企业的使用和认可,已在国内已具备 较大规模和一定品牌知名度。公司在巩固和发展现有业务的同时,重点开拓了探针台、 高端测试机产品、三温分选机、AOI 光学检测设备等相关封测设备,不断拓宽产品线, 积极开拓中高端市场。 外延方面,长川科技于 2019 年完成收购 STI,收购完成后整体经营情况良好,2019 年 和 2020 年分别实现净利润 313.20 万新元和 4,460.1 万元。2022 年长川科技拟收购长 奕科技 97.6687%股权至持股 100%,长奕科技主要经营性资产为 EXIS,EXIS 核心产品 为转塔式分选机,下游客户包括博通、MPS、NXP、比亚迪半导体、通富微电、华天科技 等国内外知名厂商。长川科技与 EXIS 在销售渠道、技术研发等领域具有较强的协同效 应,此次收购将进一步完善公司产品品类,提升公司盈利能力的同时巩固核心竞争力。 长川科技公司当前多维度拓宽业务布局,内生有机增长与外延收购并举,成长可期。

7.3 新益昌:国产固晶设备龙头,Mini LED、半导体双轮驱动成长

深耕十六年,LED 固晶龙头。新益昌成立于 2006 年,现为国内 LED 固晶机、铝电解电 容器老化测试智能制造装备领域的领先企业。至 2019 年,公司从单一的电子测试设备 和元器件的加工生产发展成拥有 LED 固晶机、半导体固晶机、电容器老化测试设备、锂 电池设备等系列产品的大型智能制造装备企业。公司 2018 年全球固晶设备市场的占有 率为 6%,位列全球第三,国内 LED 固晶机市占率约 28%,是国内 LED 固晶机领域的领 跑者。 新益昌 2022 年前三季度实现营收 10.1 亿元,yoy+26.4%,归母净利润 2.1 亿元, yoy+32.8%,扣非归母净利润 1.9 亿元,yoy+27.8%,前三季度综合毛利率 44.2%,同 比+1.1%,净利率 20.7%,同比+1.0%,公司 22Q3 单季度实现营收 3.6 亿元,yoy+19.5%, qoq+22.5%,归母净利润 0.86 亿元,yoy+50.2%,qoq+68.4%;单季度毛利率 46.2%, yoy+3.3%,qoq+0.6%,净利率 23.9%,yoy+4.8%,qoq+6.5%。

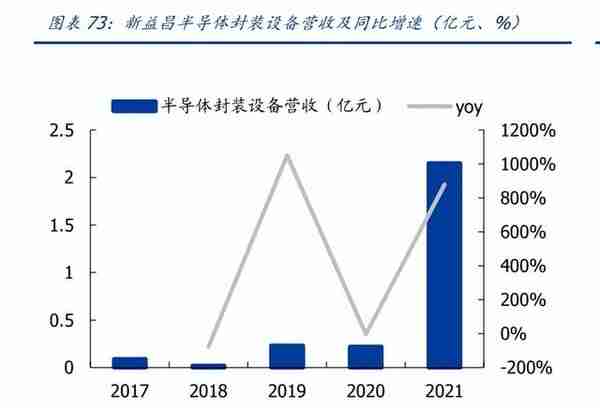

LED 固晶机和电容器老化设备是收入主要来源,半导体和锂电池收入大幅提升。2022H1, 公司营业收入 6.45 亿元,其中 LED 固晶机收入 5.21 亿元和电容器老化设备收入 1.02 亿 元,LED 固晶机和电容器老化设备占比 61.93%。2021 年,半导体封装收入 2.15 亿元, 同比增速达 877%;锂电池收入 0.31 亿元,同比增速为 63.16%。

终端应用推进超预期,奠定 Mini LED 商用元年。Mini LED 背光是液晶显示技术路径的 重要创新方向,Mini LED 显示是继 LED 户内外显示屏、LED 小间距之后 LED 显示技术 升级的新产品。当前,苹果、三星等多家品牌厂商都已开始推出 Mini LED 背光相关产品, 行业风向标的入局,推动 Mini LED 商业化加速。当前 Mini LED 背光方案已经进入爆发 期,预计 2023 年开始将有更多的相关产品出现。Mini RGB 直显注重商用显示器等市场 需求,在商业显示、电子产品装饰灯、车尾灯或气氛灯等领域具有优势,亦逐渐替代传 统的小间距等超大尺寸显示方案。 超级电容器持续渗透,锂电池带来成长新动能。超级电容器作为新型高效储能器件,广 泛应用于国防军工、轨交、发电、消费电子等重要领域。新益昌在电容器设备领域已成 为国内知名电容器厂商首选设备品牌之一。2020 年国内超级电容器市场规模为 155 亿 元,公司有望受益国内超级电容持续渗透率带来的设备需求增长。受新能源汽车带动, 锂电池尤其是动力锂电池产量保持高速增长态势,公司自 2017 年开始切入锂电池设备领域,产品已涵盖卷绕机、制片机、及制片卷绕一体机等锂电池设备,锂电池设备或将 增厚公司营收空间。

切入半导体固晶机打开新成长空间。Mini LED 对固晶设备的更高精度要求,拉动了传统 LED 封装产线升级,新益昌作为国内 LED 固晶机龙头,技术实力领先,且具备核心零部 件自研自产能力,GS300、HAD8606 系列产品逐渐成为主流的 LED 转移设备方案。三星、 鸿利智汇、国星光电、瑞丰光电等均为公司客户,预计将有更多封测厂商跟进封装转移 设备升级,公司将直接受益。在 LED 固晶机基础上,公司逐步向半导体固晶机跃迁,产 品已成功导入晶导微、灿瑞科技、扬杰科技、通富微、固锝电子等知名公司,短期受益 固晶机国产替代,长期有望横向拓展,拥抱更广阔市场空间。 固晶机和焊线机是封装中占比较高的设备。封装设备包括固晶机、焊线机、电镀设备、 减薄机、划片机等。半导体封装测试工艺流程包括磨片、划片、装片、固晶、塑封等多 个环节,其中设备价值量占比最高的为固晶机和焊线机,占比各为 28%,两者对芯片生 产过程中的良率控制至关重要。

封装市场国产化率低,外资龙头占据主导地位。封测设备市场龙头先发优势大,在该领 域内积累了数十年的经验。且下游客户对精度、稳定性和一致性要求严格,认证壁垒极 高,造就了行业内较高的集中度,龙头均为外资公司,如 ASMPT、K&S、Advantest 等。 根据 MIR DATABANK 统计,2021 年封测设备各环节综合国产化率仅为 10%,其中焊线 机、固晶机、划片机环节的国产化率最低,为 3%。预计 2025 年末综合国产化率有望达 到 18%,国产化空间广阔。

新益昌布局半导体固晶机,卡位国产替代历史性机遇。由于半导体封装和 LED 封装在流 程上具有相似性,也同样有“固晶”这道工序,公司凭借 LED 固晶领域深厚的研发实力 和持续的技术创新能力,于 2017 年开展半导体封装设备的研发,并成功推出半导体固 晶机设备。公司当前产品以功率封装为主,现已成功导入晶导微、灿瑞科技、扬杰科技、 通富微电、固锝电子等知名公司。2021 年公司半导体固晶机业务营收达 2.15 亿元,同 比增速达 877%。在当前国内半导体产业链加速推动国产替代的大趋势下,公司有望深 度受益,巩固竞争优势,进一步推动半导体固晶机国产替代。

焊线机技术门槛高,价值量占封装设备市场 32%。引线键合作为封装环节最关键的步 骤之一,具有极高的技术壁垒,使用的焊线设备对速度、精度、稳定性有严格要求,核 心难点在于控制引线在焊盘的键合质量以及引线在三维空间的线弧轨迹。根据 SEMI 研 究统计,在半导体前道与后道工序的全生命周期制程中,封装设备约占半导体设备市场 规模的 6%,其中焊线机占封装设备市场规模的 32%。按此测算,焊线机占半导体制程 设备市场规模的比重为 1.92%,全球焊线机市场规模由 2015 年的 7.01 亿美元增长至 2022 年的 21.95 亿美元,2015-2022 年年均增速为 17.71%。 焊线机市场高度集中,CR3 超 95%。焊线机市场被外资长期垄断,市占率前三位 K&S、 ASM 和 Kaijo,市占率分别为 60%、30%、8%。K&S 全称为 Kulicke&Soffa,自动焊线 机产品近五年的市场占有率都超过了 60%,近年来通过战略收购和自主研发,增加了先 进封装、电子装配、楔焊机等产品,同时配合其核心产品扩大其耗材的产品范围,进一 步巩固了其焊线机龙头地位。

7.4 长电科技:国产封测龙头,先进封装注入成长新动力

长电科技是国内封装测试龙头厂商,主营业务为集成电路、分立器件的封装与测试。为 海内外客户提供涵盖封装设计、焊锡凸块、针探、组装、测试、配送等一整套半导体封 装测试解决方案。目前公司产品主要有 QFN/DFN、BGA/LGA、FCBGA/LGA、FCOL、SiP、 WLCSP、Bumping、MEMS、Fan-out eWLB、POP、PiP 及传统封装 SOP、SOT、DIP、TO 等多个系列。 八大基地布局,全面覆盖高中低端产品。公司目前可以分为长电本部及旗下子公司星科 金朋与长电韩国。长电本部包括江阴基地、滁州厂、宿迁厂与长电先进四个生产基地, 星科金朋包括星科金朋江阴、星科金朋新加坡与星科金朋韩国,此外长电韩国(JSCK) 为长电科技在韩国新设立的 SIP 封装厂,主要是为了配合星科金朋韩国(SCK),共同开 拓国内外客户。

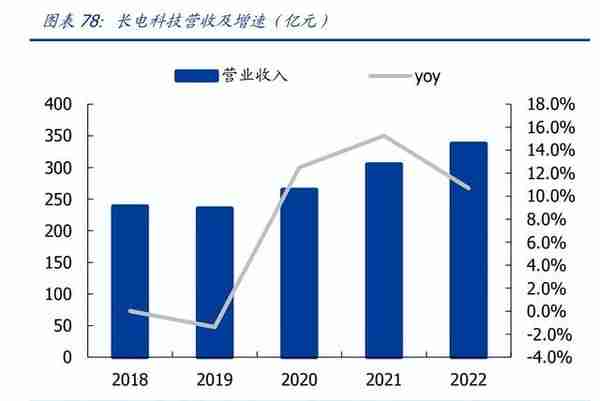

长电科技发布 2022 年报。公司 2022 年全年实现营收 337.62 亿元,yoy+10.69%,归 母净利润 32.31 亿元,yoy+9.20%,扣非归母净利润 28.30 亿元,yoy+13.81%,全年 综合毛利率 17.04%,同比-1.37%,净利率 9.57%,同比-0.13%。面对半导体市场周期 下行,公司通过积极灵活调整订单结构和产能布局,推进产品结构优化,加速从消费类 向市场需求快速增长的汽车电子,5G 通信,高性能计算、存储等高附加值市场的战略布 局,持续聚焦高性能封装技术高附加值应用,实现了稳健的增长。 分下游应用领域来看,公司 2022 年营收中通讯电子占比 39.3%、消费电子占比 29.3%、 运算电子占比 17.4%、工业及医疗电子占比 9.6%、汽车电子占比 4.4%,与去年同期相 比消费电子下降 4.5 个百分点,运算电子增长 4.2 个百分点,汽车电子增长 1.8 个百分 点。测试领域,公司引入 5G 射频,车载芯片,高性能计算芯片等更多的测试业务,相关 收入同比增长达到 25%。

7.5 通富微电:AMD 加持,产品结构持续优化

通富微电发布 2022 年报。公司 2022 年全年实现营收 214.29 亿元,yoy+35.52%,公 司积极调整产品业务结构,加大市场调研与开拓力度,持续服务好大客户,凭借 7nm、 5nm、FCBGA、Chiplet 等先进技术优势,强化与 AMD 等行业领先企业的深度合作,巩 固和扩大先进产品市占率。公司 2022 年实现归母净利润 5.02 亿元,yoy-47.53%,扣非 归母净利润 3.57 亿元,yoy-55.21%,全年综合毛利率 13.90%,同比-3.26%,净利率 2.34%,同比-3.71%。受汇率波动影响,公司产生汇兑损失,因此减少归属于母公司股 东的净利润 2.11 亿元,此外由于半导体周期下行,部分终端产品需求疲弱,对公司产能 利用率和毛利率产生不利影响,与此同时公司持续加大 Chiplet 等先进封装技术研发创 新投入,短期研发费用增加对利润有一定影响,长期公司高端产品占比有望持续提升。

先进封装技术领先,多样化布局。公司提前布局多芯片组件、集成扇出封装、2.5D/3D 等 先进封装技术方面,可为客户提供多样化的 Chiplet 封装解决方案,并且已为 AMD 大规 模量产 Chiplet 产品。FCBGA 封装技术方面行业领先,已完成 5nm 制程的 FC 技术产品 认证,逐步推进 13 颗芯片的 MCM 研发,FCBGA-MCM 高散热技术方面具备了 Indium TIM 等行业前沿材料的稳定量产能力。Fanout 技术达到世界先进水平,高密度扇出型封 装平台完成 6 层 RDL 开发;2.5D/3D 先进封装平台取得突破性进展,BVR 技术实现通线 并完成客户首批产品验证,2 层芯片堆叠的 CoW 技术完成技术验证。 定增落地,积极扩产迎接产业机会。公司 2022 年定增募集资金总额 26.9 亿元,拟用于 存储器芯片封装测试生产线建设项目、高性能计算产品封装测试产业化项目、5G 等新一 代通信用产品封装测试项目、圆片级封装类产品扩产项目、功率器件封装测试扩产项目、 补充流动资金及偿还银行贷款。募投项目均围绕公司主营业务展开,产能释放将助力公 司更好的抓住市场机遇,满足客户持续增长的需求,同时规模优势凸显,持续提升公司 核心竞争力,支撑公司长期增长。

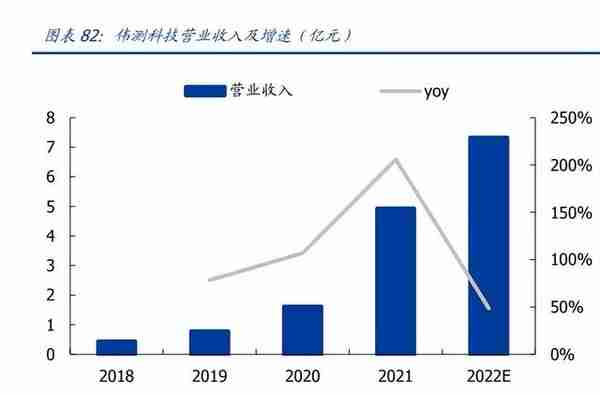

7.6 伟测科技:内资第三方集成电路测试领先厂商

伟测科技成立于 2016 年,是国内知名的第三方集成电路测试服务企业,主营业务包括 晶圆测试、芯片成品测试以及与集成电路测试相关的配套服务。公司测试的晶圆和成品 芯片在类型上涵盖 CPU、MCU、FPGA、SoC 芯片、射频芯片、存储芯片、传感器芯片、 功率芯片等芯片种类,在工艺上涵盖 6nm、7nm、14nm 等先进制程和 28nm 以上的成 熟制程。目前公司已布局 5G 通讯、智能穿戴、传感器、存储等芯片的测试解决方案产 品,拥有国际先进水平的集成电路测试装备,可以覆盖市场上 80%的主流集成电路产品 的检测。 客户资源优质。公司坚持“以晶圆测试为核心,积极发展中高端芯片成品测试”的差异 化竞争策略,成为第三方集成电路测试行业成长性最为突出的企业之一。公司的技术实 力、服务品质、产能规模获得了行业的高度认可,积累了广泛的客户资源。目前公司客 户数量超过 200 家,客户类型覆盖芯片设计、制造、封装、IDM 等,其中包括紫光展锐、 中兴微电子、晶晨半导体、中颖电子、比特大陆、卓胜微、兆易创新、长电科技、中芯 国际等国内外知名厂商。

IPO 募投加码集成电路测试产能扩充及研发投入。公司上市募集资金约 6.1 亿元,用于 无锡伟测扩产及集成电路测试研发中心项目,及补充流动资金。公司持续投入研发,提 升技术水平,增厚壁垒,保持核心竞争力,在强大的客户资源基础上,公司测试产能的 扩充,为长期发展提供重要支撑。

7.7 甬矽电子:封测界后起之秀,聚焦中高端业务

聚焦先进封装,产品结构完善优质。甬矽电子成立于 2017 年 11 月,主要聚焦集成电路 封测中的先进封装领域,主要终端包括消费类电子、汽车电子、工规产品等。公司在国 内独立封测企业中排名第 11,在内资独立封测企业中排名第 6,技术实力和规模均在前 列。且销售收入主要来自于中高端封装产品,并在射频前端芯片封测、AP 类 SoC 芯片封 测、触控 IC 芯片封测、WiFi 芯片封测、蓝牙芯片封测、MCU 等物联网(IoT)芯片封测 等新兴应用领域具有良好的市场口碑和品牌知名度。 坚持研发,技术独立自主。截至 2022 年 6 月 30 日,公司已经取得的专利共 186 项,其 中发明专利 88 项、实用新型 96 项、外观专利 2 项。2019 年-2022 年 6 月,公司研发投 入金额分别为 2,826.50 万元、4,916.63 万元、9,703.86 万元和 6,021.12 万元,呈稳定 上升趋势。未来公司将根据自身发展战略和市场需求情况,继续加大研发投入力度,持 续完善研发人员储备战略,提高研发人员的专业能力。公司在高密度细间距凸点倒装产 品(FC 类产品)、系统级封装产品、4G/5G 射频功放封装技术、高密度大尺寸框架封装 产品、MEMS 封装产品、IC 测试等领域均具拥有核心技术,且稳定量产。

IPO 募集资金投资额 15 亿元,分别用于高密度 SiP 射频模块封测项目、集成电路先进 封装晶圆凸点产业化项目。一方面缓解产能瓶颈,提高市占率,另一方面可完善倒装类 封装产品制程,补全公司生产工艺短板,为 Fan-Out、WLCSP 等拟开发的先进封装产品 提供工艺支持。公司现有的 SiP 等先进封装技术是 Chiplet 模式的重要实现基础,Chiplet 模式的兴起有望驱动先进封装市场快速发展。公司在 SiP 领域具备丰富的技术积累,同 时通过实施晶圆凸点产业化项目布局“扇入型封装”(Fan-in)、“扇出型封装”(Fan-out)、 2.5D、3D 等晶圆级和系统级封装应用领域,为进一步拓展异构封装领域打下基础。

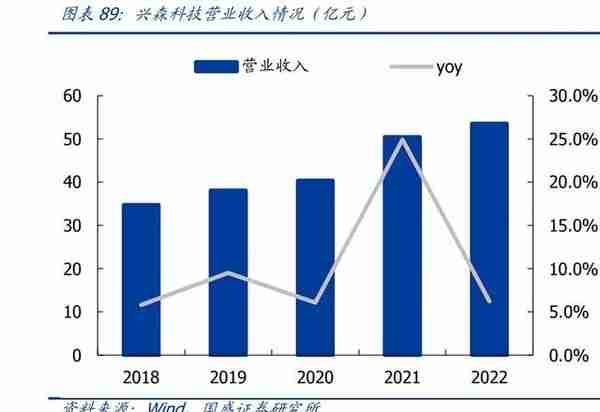

7.8 兴森科技:IC 载板国产替代拓荒者

兴森科技成立于 1999 年,目前主营业务围绕 PCB 以及半导体这两大业务主线开展。兴 森科技一直致力于国内外高科技电子企业和科研单位的服务,产品下游应用领域十分之 广。另外公司也通过 PCB 样板所积累下来的领先技术优势,深入 IC 载板领域,并开拓 半导体测试板业务;同时积极拓展 PCB 批量板产能,与 PCB 样板业务实现协同,将自身 打造成 PCB 一站式解决厂商;此外半导体测试板及 IC 封装基板也帮助公司实现半导体 封装测试领域的国产替代领先者。 兴森科技:乘胜追击,产能扩张正当时。目前公司主要在建项目包括珠海兴科项目、宜 兴硅谷印刷板二期工程项目和广州 FCBGA 封装基板生产和研发基地项目。珠海兴科项目 中,第一条 IC 封装基板的产线(1.5 万平方米/月)进展顺利,预计年底实现单月 90%以上的产能利用率。宜兴生产基地二期工程完全达产后,将提供 96 万平方米/年的产能, 产品将应用于 5G 通信、Mini LED、服务器和光模块等领域。广州生产基地于 2021 年新 增了月产 1.5 万平方米的中、高端、多层样板的产线,目前,其中 7,000 万平方米/月产 能已达产。公司在 2022 年宣布了位语广州和珠海两个 FCBGA 项目投资,广州项目预计 于 2023 年底前后建成,目前正在进行前期建设准备工作和设备采购。

兴森科技为国内为数不多的 IC 载板厂商,大力扩产载板产能用以满足行业需求,进行 国产替代及对新增市场的占领。根据公司公告,广州兴科 BT 载板、广州和珠海 FCBGA 封装基板项目的整体投资规模为 102 亿,有望看到公司未来实现 IC 载板产品线的全覆 盖,随着公司新增载板产能逐步爬坡投产,以及行业当前供需紧张的态势,有望充分受 益国内半导体的巨大封装需求,加速提升载板业务的收入规模和贡献业绩。 公司 2022 年全年实现营收 53.54 亿,同比增长 6.23%;归母净利润 5.26 亿,同比下降 15.42%,主要是因为 PCB 行业面临需求不振和竞争加剧的双重压力,增长不达预期, FCBGA 封装基板项目仍处于建设阶段,未产生收入贡献,但整体人工成本、研发投入、 试生产损耗等对公司利润形成较大拖累,FCBGA 封装基板项目全年费用投入约 1.02 亿 元。

兴森 2022 年 12 月 17 日公告,深圳市兴森快捷电路科技股份有限公司同意公司全资子 公司广州兴森投资有限公司以 176.61 亿日元(税前,按 20.3 日元=1 元人民币的汇率计 算为 8.7 亿元人民币,定价基准日为 2022 年 6 月 30 日)作为基础购买价格(将就净资 产变动额等调整项对基础购买价格进行调整)收购揖斐电株式会社(Ibiden Co,Ltd.) 持有的揖斐电电子(北京)有限公司 100%股权。本次交易完成后,兴森投资将持有北 京揖斐电 100%的股权,北京揖斐电将成为公司全资孙公司,纳入公司合并报表范围。 未来,公司计划引入其他战略股东入股北京揖斐电共谋发展,持续加大研发力度,并增 加对先进设备和工艺的投资,推进产品和技术的持续升级,提高其产品附加值。 北京揖斐电是揖斐电于 2000 年 12 月在北京经济技术开发区注册成立的全资子公司,其 专注于面向移动通讯用印制电路板产品,以高性能微小导孔和微细线路的高密度互连电 路板(普通 HDI 和 Anylayer HDI)为主要产品,主要应用于智能手机、可穿戴设备、平 板电脑等消费类终端电子产品,与国内外主流手机厂商在高端印制电路板产品领域建立 了稳定的合作关系。近年来持续投入以促进产品和技术升级,开发并量产 mSAP 流程的 类载板(SLP)和模组类封装基板产品,丰富了产品线并进一步巩固了其在客户群体中高 端印制电路板领先厂商地位。

(本文仅供参考,不代表我们的任何投资建议。如需使用相关信息,请参阅报告原文。)

精选报告来源:【未来智库】。「链接」

推荐阅读

-

美元和中国人民币汇率(美元与中国汇率)

2023-05-24

面对半导体市场周期 下行,公司通过积极灵活调整订单结构和产能布局,推进产品结构优化,加速从消费类 向市场需求快速增长的汽...

-

社保激费基数包括(社保的激纳基数有什么用)

2023-05-24

面对半导体市场周期 下行,公司通过积极灵活调整订单结构和产能布局,推进产品结构优化,加速从消费类 向市场需求快速增长的汽...

-

四川信托股权拍卖(四川信托股权拍卖公告)

2023-05-24

面对半导体市场周期 下行,公司通过积极灵活调整订单结构和产能布局,推进产品结构优化,加速从消费类 向市场需求快速增长的汽...

-

建行信用卡龙卡visa(建行信用卡龙卡为什么有两张)

2023-05-24

面对半导体市场周期 下行,公司通过积极灵活调整订单结构和产能布局,推进产品结构优化,加速从消费类 向市场需求快速增长的汽...

-

银行承兑汇票贴现天数怎么算(银行承兑汇票的贴现期限)

2023-05-24

面对半导体市场周期 下行,公司通过积极灵活调整订单结构和产能布局,推进产品结构优化,加速从消费类 向市场需求快速增长的汽...

-

格力电器股票十年行情(格力电器股票十年行情走势图)

2023-05-24

面对半导体市场周期 下行,公司通过积极灵活调整订单结构和产能布局,推进产品结构优化,加速从消费类 向市场需求快速增长的汽...